# **MUSIC COMPUTER** CX-5M II

# SERVICE MANUAL

CX-5MIIC CX-5MIIE CX-5MIIF CX-5MIIA CX-5MIIB CX-5M∏P

#### **CONTENTS**

| MSX COMPUTER ACCORDING TO AREA 1       |

|----------------------------------------|

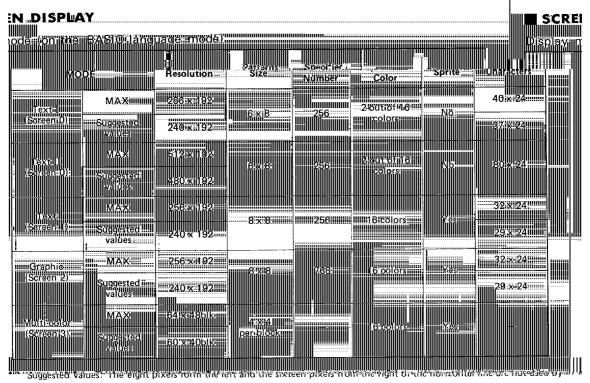

| SCREEN DISPLAY 1                       |

| SPECIFICATION 2                        |

| CX-5MII BRIEF DESCRIPTION              |

| MUSIC FUNCTIONS (SFG-05 COMPATIBLE) 7  |

| MIDI RECEIVING AND TRANSMITTING DATA 8 |

| SLOT A AND SLOT B ASSIGNMENT 10        |

| DISASSEMBLY PROCEDURES 11              |

| ADJUSTMENTS 15                         |

| OPERATION OF POWER SUPPLY CIRCUIT 16   |

| LSI DATA TABLE                         |

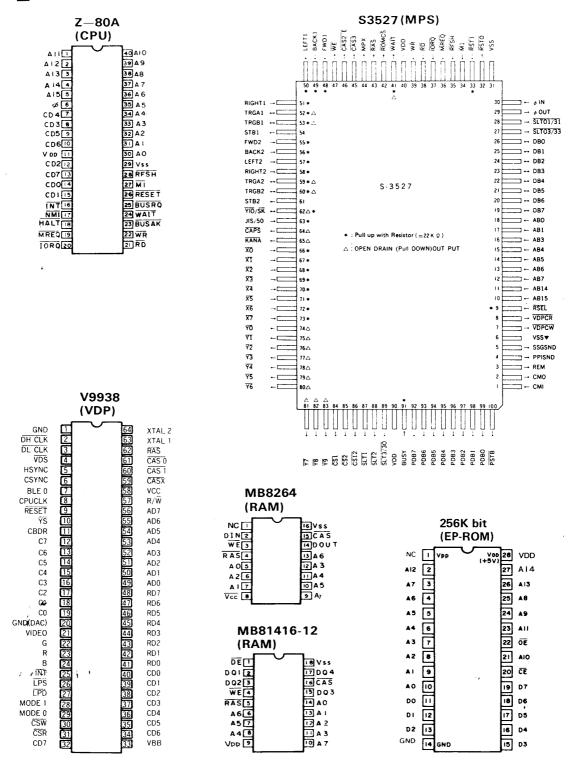

| LSI PIN CONFIGURATION                  |

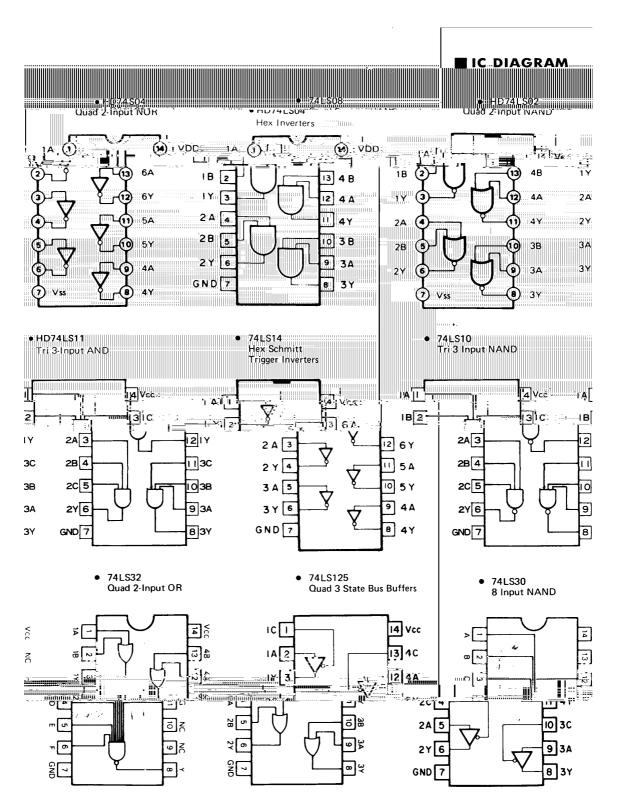

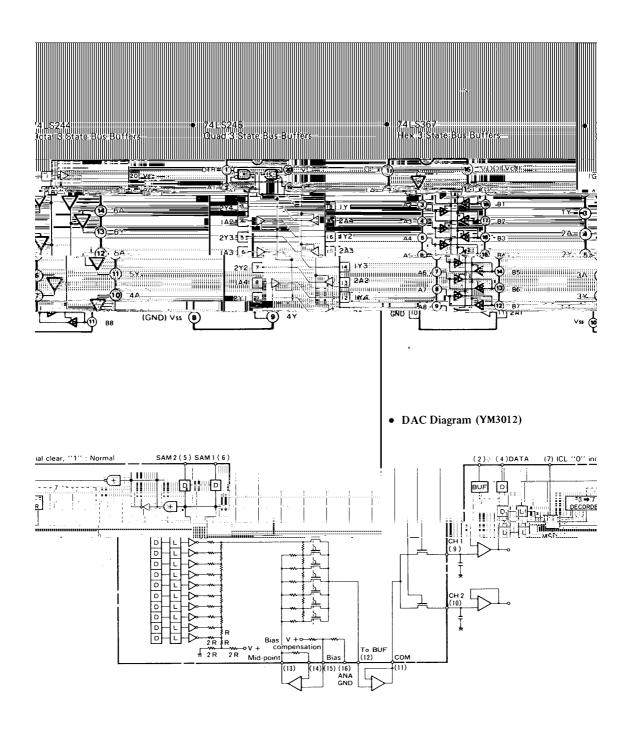

| IC DIAGRAM 23                          |

| PARTS LIST                             |

008511

Scanned by Jean-Pierre Dubois, converted to pdf by MSXHans, 2001

# *ICCORDING TO AREA*

YAMAHA MSX COMPUTER according to area, this manual refer to the II, referring to all models. Where reference to particular model is called for retaining to the area in question will be used. The different model numbers, retain, are as follows.

| Canada   | (NTSC)                    |         |

|----------|---------------------------|---------|

| CX-bMlie | Ünited Kingdom (T         | (PAL=1) |

| CX-5MIIA | Australia and New Zealand | (PAL-B) |

| CX-5MIIF | France                    | (PAL-G) |

| CX-5MIIB | Italy                     | (PAL-G) |

| CX-5MIIP | Spain                     | (PAL-G) |

# ■ MSX COMPUTER /

There are different models of computer as only the CX-5M the specific model number pe and the area to which they pe

CX-5MIIC . . . .

#### **SPECIFICATION**

CPU Type:

LH0080A (Z80A compatible)

Clock: Wait:

3 579545MHz 1 wait in M1 cycle

NMI-not used Interrupt:

INMI-not used INT-accept interrupts from VDP and cartridge SLOT The interrupt mode is Z80 mode 1. The interval of the interrupt is 50Hz (NTSC: 60Hz).

Power on reset and reset switch.

Reset: MEMORY

> Main Memory: (RAM) BASIC ROM:

128 Kbyte (128 Model)

64 Kbyte ( 64 Model) 32 Kbyte (MSX1-BASIC) 16 Kbyte (for 80 Chara) 16 Kbyte

Sub ROM: Video RAM:

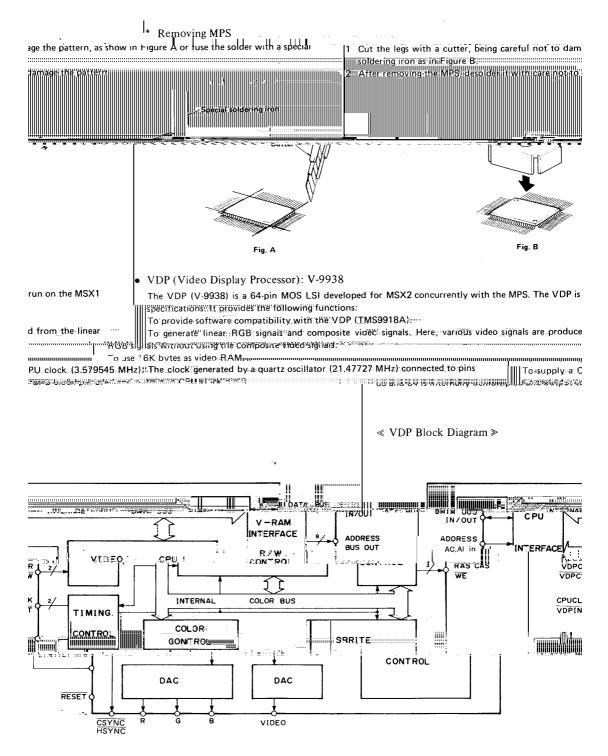

VIDEO DISPLAY Video Display Processor (VDP) V9938

Type:

Character Set: Color:

256 alphanumeric and graphic characters

16 colors

SCREEN 0 or SCREEN 1 Text mode: Capability:

24 lines by up to 80 columns (Software selectable)

Resolution:

256 x 192 pixels (non interlace)

INPUTS AND OUTPUTS

Keyboard:

Stroke type step sculpture keyboard. Stroke type step sculpture keyboard.

Alphanumeric and special characters . 48

Control and special effect keys . . . 16

Cursor movement keys . . . . 4

Function keys (programmable) . . . 5

CAPS lock key with LED indicator

Cassette Interface:

8 pin DIN female connector

Baud rate 1200/2400 BPS selectable by

software, FSK format. With remote

control (Cassette motor ON/OFF)

Printer Interface:

Standard centronics 8-bit parallel TTL

logic level 14 pin female connector

Univarsal I/O Interface:

2 ports (JOYSTICK) 9 pin male connectors TTL logic level

Audio/Video Output:

1) MONITOR output

RCA type pin connector

CX-5MIIE, F, A, B, P

PAL composite video output 75

ohm

CX-5MIIC

NTSC composite video output 75

ohm

2) SOUND output

RCA type pin connector CX-5MIIC, E, F, A, B, P 8 octaves 3 tones + noise BEEP sound

BEEF Sound

3) RF output

RCA type pin connector

CX-5MIIC: NTSC (VHF3, 4)

CX-5MIIA: PAL (VHF3, 4)

CX-5MIIE, F,B,P:PAL (UHF36)

4) RGB output

8 pin DIN female connector

CX-5MILC, E, F, A, B, P

5) Color or Block/White switch

Monitor and RF output used

Upper SLOT A, B:

SLOT 1, 2 50 pin MSX standard female con-

nector

SIDE SLOT:

60 pin edge card connector FM

sound unit

BILT in ROM SOCKET: SLOT 30

30 pin plug right ungle type

FM SOUND SYNTHESIZER UNIT

Number of Preset Voices: 46

Simultaneous Notes: Up to 8 notes

Audio L/R Outputs:

$-9 \pm 2 dB$ , 1.8k $\Omega$  RCA-pin jacks 5 pin DIN female connectors

MIDLIN/OUT:

For connection to an optional YK-01 or Music Keyboard:

YK-10, 20 music keyboard. 20 pin male connector

POWER SUPPLY UNIT CAPACITY

+5V ± 5% 2.0A +12V ± 10% 0.3A -12V ± 10% 0.16A

**GENERAL SPECIFICATIONS**

Line voltage:

CX-5MIIC 117V±15%, 50/60Hz CX-5MIIE, F, A 220 ~240V, 50/60Hz CX-5MIIB, P 120V±10%, 50/60Hz 220V±10%, 50/60Hz Switchable

Switchable

Power input: 10W 18W MAX

440(W) x 285(D) x 98(H) Measurement:

Weight: 3.5 kg (about) AC cable:

2,000 mm + 50 mm with AC plug (CX-5MIIC, F, A, B, P)

# ■ CX-5MII BRIEF DESCRIPTION

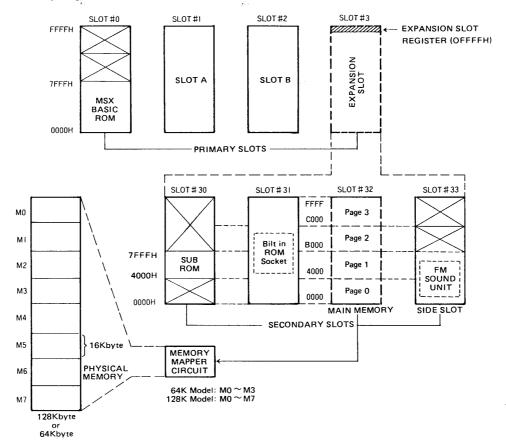

# • Memory map and slot area

Terminology: Primary slot . . . . Slot which is enabled by slot select register with in MPS chips (I/O address 0A8H)

Secondary slot . . . Slot which is enabled by expansion slot register placed at 0FFFH (Memory address)

Page . . . . . . . . . Block of memory (maximum 16KB) in each slot. A slot is divided into 4 pages.

\* Every select signal of each slot is output from MPS (100 pin LSI: S-3527)

MSX BASIC ROM . . . . . . ROMCS

\* With the memory mapper circuit, the block by the unit of 16K bytes in the PHYSICAL MEMORY space can be mapped freely on each page of the MAIN MEMORY space.

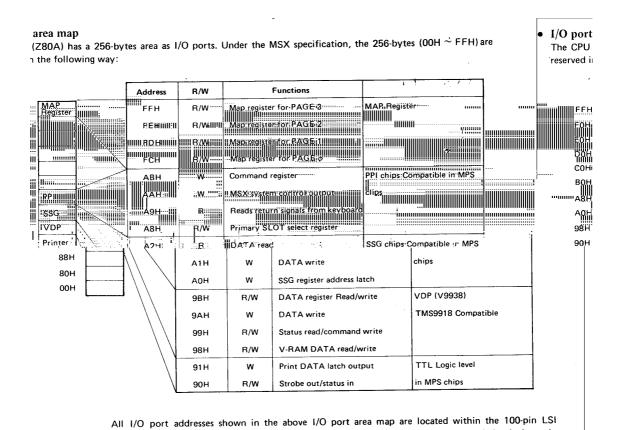

# MPS (S-3527) I/O ports register

I/O address A8H (PAO ~ PA7): Slot select data register

A9H (PB0  $\sim$  PB7): Keyboard scanning data input (return) port

AAH (PC0  $\sim$  PC3): Keyboard scanning data output port

(PC4): Data recorder (cassette recorder) motor ON/OFF control bit (PC5): Output FSK specification data to data recorder (cassette)

(PC6): CAPS LED control bit (on when "L") (PC7): Emits beeping sound through 1 bit output

the map. In addition, it has memory area and slot control functions.

I/O address A0H  $\sim$  A2H

Internal SSG register number: 10H

(IOA0 ~ IOA5): Input port for general purpose. Input/output port (JOYSTICK 1, 2) data scanning.

(S-3527). The LSI encloses the  $\mu PD$ -8255A (PPI), YM2149 (SSG), and printer control circuit shown in

(IOA6): Not used

(IOA7): Input port for data from data recorder (cassette).

Internal SSG regester number: 11H

(IOB0  $\sim$  IOB3): JOYSTICK port scanning data output. (IOB4): JOYSTICK 1 strobe signal output.

(IOB5): JOYSTICK 2 strobe signal output. (IOB6): JOYSTICK 1 or 2 select signal

"L" .... JOYSTICK 1 selected

"H" .... JOYSTICK 2 selected

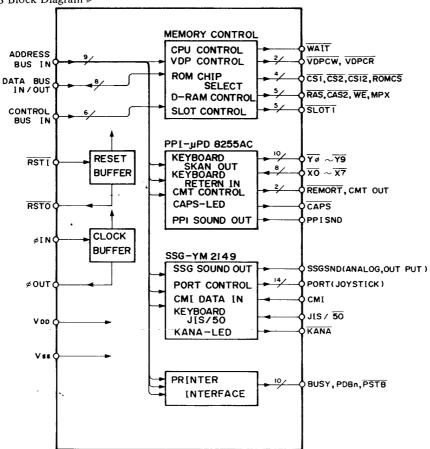

• MPS (MSX Port Controller and Sound Generator): S-3527

# D-8255) and

The MPS (S-3527) is a 100-pin CMOS LSI specifically developed to support MSX. With a built-in PPI ( $\mu$ P SSG (YM-2149), the MPS provides the following system controller functions:

- Memory and slot area control

- ROM (MSX-BASIC ROM: 32K bytes) access ROMCS

- RAM (D-RAM: 64K bytes) access

RAS, MPX, WE, CAS2

- Basic slot (# 1, # 2, # 3) control . . . Primary slot control

- Selection and control of expansion slots (# 00, # 01, # 02, # 03) . . . Secondary slot

- I/O area (I/O peripheral) control

- Printer control

- BUSY, PDBn, PSTB

- VDP (video dispiay processor) control VDPCW, VDPCR

- With a built-in PPI (μPD-8255) and SSG (YM-2149)

- ...•13-Channel 3-level voice-and noise autout

- Dual joystick (or general-purpose port) control

- Data recorder I/O control

- Keyboard control

- Insertion of 1 WAIT in the CPU M1 cycle

- RESET signal processing

- CPU clock (3.57954 MHz) input

#### « MPS Block Diagram »

#### ■ MIDI RECEIVING AND TRANSMITTING DATA

The unit receives the following MIDI signals (when CALL MUSIC is functioning).

#### MIDI receiving data

### Channel message

ignals

When the MIDI receiving channel is specified for each instrument, the unit receives the following MIDI stransmitted through the specified channel.

① Key-OFF

② Key-ON

3 Control change

Status  $1 \ 0 \ 1 \ 1 \ n \ n \ n \ (B \ n \ H)$   $n = channel \ No.$  Control No.  $0 \ c \ c \ c \ c \ c \ c$   $c = control \ No.$

Control Nalue ו

C = 5 Portamento time (SOLO mode only) (iii)

C = 7 Volume and

C = 64 Sustain switch

C = 65 Portamento switch (SOLO mode only)

.\_\_\_\_C=325 Al notes OFF if

4 Program change

#### • System real time message

The unit receives the following system real time messages when the play clock is MIDI.

① Timing clock

Status 1 1 1 1 1 0 0 0 (F 8 H)

② Start Status

11111010(FAH)

3 Continue start

Status 1 1 1 1 1 0 1 1 (F B H)

4 Stop

Status 1 1 1 1 1 0 0 (F C H)

### • MIDI transmitting data

The unit transmits the content played by the music keyboard and reproduction data through MIDI channel 1.

#### • Channel voice message

#### ① Key-OFF/Key-ON

Status 1 0 0 1 0 0 0 0 (90 H)

11111010(FAH)

### • System real time message

The unit outputs the following system real time messages when the play clock is INTERNAL.

① Timing clock

Status

3 Stop

Status 1 1 1 1 1 1 0 0 (F C H)

# **DT A AND SLOT B ASSIGNMENT**

|       | Pin Na                                 | ame        | I/O     |                                                            | Description                                              | Pir        |  |  |

|-------|----------------------------------------|------------|---------|------------------------------------------------------------|----------------------------------------------------------|------------|--|--|

|       | CS                                     | 1          | 0       | Select                                                     | Signal for ROM 4000H-7FFFH                               | 1          |  |  |

|       | CS:                                    |            | o       |                                                            | Signal for ROM 8000H-BFFFH                               | 2          |  |  |

| ł     | CS1                                    |            | ō       |                                                            | Signal for ROM 4000H-BFFFH                               | 3          |  |  |

| - 1   | SLT                                    |            | õ       |                                                            | elect Signal                                             | 1 4        |  |  |

|       | N/C                                    |            | _       |                                                            | ted to use                                               | 5          |  |  |

| 1     | RES                                    |            | 0       |                                                            | ic RAM refresh signal                                    | 6          |  |  |

| İ     | EXT W                                  |            | ĭ       |                                                            | request, open collector signal                           | 7          |  |  |

| - 1   | EXT                                    |            |         |                                                            | ble interrupt request, open collector signal             | 8          |  |  |

| 1     | M                                      |            | o l     |                                                            | nal from CPU                                             |            |  |  |

| 1     | BUSE                                   |            | i       |                                                            | ion Control for external 3us Buffer                      | 9          |  |  |

| - 1   |                                        |            | o       |                                                            | quest from CPU                                           | 10         |  |  |

| 1     | TOR                                    |            |         |                                                            |                                                          | 11         |  |  |

| - 1   | WE                                     |            | 0       |                                                            | al memory request from CPU                               | 12         |  |  |

| Ì     |                                        |            | 0       |                                                            | request from CPU                                         | 13         |  |  |

|       | <u>RD</u>                              |            | 0       |                                                            | request from CPU                                         | 14         |  |  |

|       | RES                                    |            | 0       |                                                            | n Preset signal                                          | 15         |  |  |

| 5     | N/ <u>(</u>                            | Ŷ <b>.</b> | ⊞iiiiii | Inhibi                                                     | ted to use                                               | ≣16<br>-17 |  |  |

|       |                                        |            |         | ,                                                          |                                                          | 1 =17      |  |  |

| 딕     | A1                                     |            | 0       | · • •                                                      |                                                          | 18         |  |  |

| - III | A1                                     |            | 0       |                                                            | i                                                        | 19         |  |  |

|       | A10                                    |            | 0       | · I i                                                      | 1 · i                                                    | 20         |  |  |

|       | 21:                                    | A          |         | ₫.:                                                        |                                                          |            |  |  |

|       | 22                                     | А          |         | 0:                                                         |                                                          |            |  |  |

|       | 23                                     | <b>A</b> 1 |         | 0:                                                         |                                                          |            |  |  |

|       | 24                                     | Α          |         | 0.                                                         |                                                          |            |  |  |

|       | 25                                     |            | 14.     | 0.                                                         | >Address Bus signal                                      |            |  |  |

|       | 26                                     | Α1         | 13      | 0:                                                         | [*]                                                      |            |  |  |

|       | 27.                                    | Α          | 1       | 0.                                                         | ·                                                        |            |  |  |

|       | 28                                     | А          | 0 .     | 0                                                          |                                                          |            |  |  |

|       | 29                                     | Α          | 3       | ···· 0:                                                    | P¦                                                       |            |  |  |

|       | 3C:                                    | A·         | 2:      | 0:                                                         | i!                                                       |            |  |  |

|       | 31                                     | ,          | 45 '    | 0                                                          |                                                          |            |  |  |

|       | 32                                     | ,          | 44      | 0                                                          | J                                                        |            |  |  |

|       | 33                                     | (          | D1      | 1/0                                                        |                                                          |            |  |  |

|       | 34                                     | [          | 00      | 1/0                                                        | 1                                                        |            |  |  |

|       | 35                                     | 1          | D3      | 1/0                                                        |                                                          |            |  |  |

|       | 36                                     | (          | 02      | 1/0                                                        | Data Bus signal                                          |            |  |  |

|       | 37                                     | 1          | D5      | 1/0                                                        |                                                          |            |  |  |

|       | 38                                     |            | 04      | 1/0                                                        |                                                          |            |  |  |

|       | 39                                     |            | 57      | 1/0                                                        |                                                          |            |  |  |

|       | 40                                     | (          | D6      | 1/0                                                        |                                                          |            |  |  |

|       | 41                                     | G          | ND      | _                                                          | Ground                                                   |            |  |  |

|       | 42                                     | CL         | OCK     | 0                                                          | System Clock 3,579545MHz                                 |            |  |  |

|       | 43                                     |            | ND      | _                                                          | Ground                                                   |            |  |  |

|       | 44                                     |            | W1      | -                                                          | System protection                                        |            |  |  |

|       | 45                                     |            | +5      | -                                                          | Power Supply +5V                                         |            |  |  |

|       | 46                                     |            | W2      | System protection (Note: SW1 and SW2 is in connection when |                                                          |            |  |  |

|       | "                                      | •          | _       | 1                                                          | Cartridge is inserted.)                                  |            |  |  |

|       | 47                                     |            | +5      | _                                                          | Power Supply +5V                                         |            |  |  |

|       | 48                                     |            | -12     | _                                                          | Power Supply +12V                                        |            |  |  |

|       | 49                                     |            | ND IN   | 1                                                          | Sound input line (-5dbm) mixed with PSG sound and output |            |  |  |

|       | 50                                     |            | -12     |                                                            | Power Supply –12V                                        |            |  |  |

|       | ــــــــــــــــــــــــــــــــــــــ |            |         | 1                                                          |                                                          |            |  |  |

|       |                                        |            |         |                                                            |                                                          |            |  |  |

# • SIDE SLOT assignment

| Pin<br>No. | Pin Name  | 1/0 | Description                  |

|------------|-----------|-----|------------------------------|

| 1          | SOUND OUT | 0   | Mixing Sound out of SSG, PP1 |

| 2          | GND       | -   | Ground                       |

| 3          | GND       | -   | Ground                       |

| 4          | NC        | -   |                              |

| 5          | NC        | - 1 | Non connect                  |

| 6          | NC        | -   |                              |

| 7          | VIDEO     | 0   | Video Out                    |

| 8          | NC        | -   |                              |

| 9          | NC        | - [ | Non connect                  |

| 10         | NC        | -   |                              |

| 11 ~ 60    | 1100      |     | Exactly same as regular slot |

■ SL

# **PROCEDURES**

ith Repair:

or cover.

e center of the bottom case.

M cartridge cover. If a ROM cartridge has been installed, remove it also.

tery cover, remove the battery. (only MSX<sub>2</sub> Version)

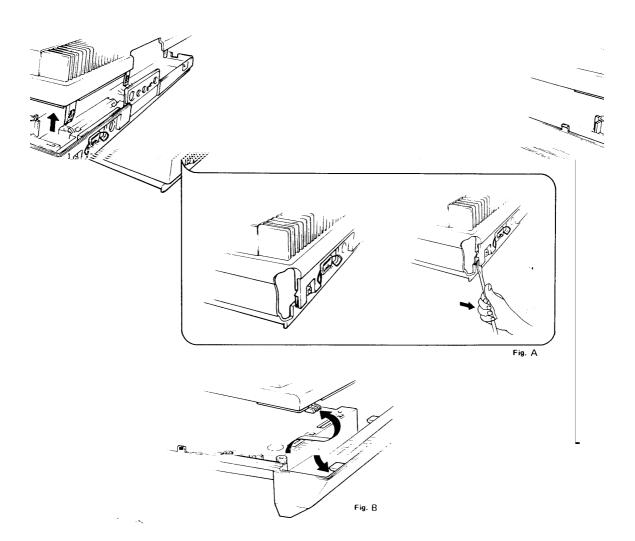

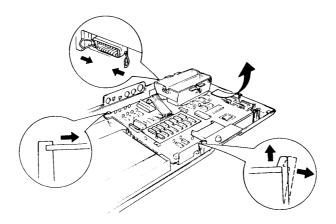

ed by pushing it at claws with a standard screwdriver as shown in Figure A. There are four claws.  $\epsilon$ .

our claws, detach the top case by lifting it a little on the rear side. The top case is fixed on the shown in Figure B. Never use undue force to release it.

# ■ DISASSEMBLY

- Before Proceeding w.

- 1 Detach the side slot unit

- 2 Remove the screw in the

- 3 Remove the built-in RO

- 4 Uncover the backup bat

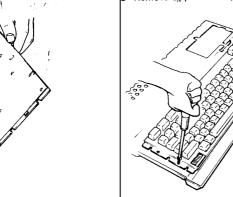

# 1) Top Case Removal

- 1 The top case can be lift Release them one by one

- 2 After releasing all the fifront side at the claw as

# 2) Keyboard Unit Removal

- 1 Remove four screws on both sides (four in total) of the keyboard unit.

- 2 Lift off the keyboard unit, slowly removing the flat cable from the CPU circuit board.

- 3 Remove Upper shield (only CX-5MIIU, G)

tall them.

# • Board and Unit Removal Procedures

Remove the boards and units in the following sequence. Reverse the removal procedures to reins

- Step 1) Power supply unit removal

- Step 2) Video module unit removal

- Step 3) Side slot earth plate removal

- Step 4) Main CPU board removal

- Step 5) Bottom shield removal

# (power switch and power

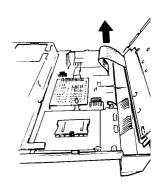

#### 3) Power Supply Unit Removal

1iiiiPüllloutiithe:power.connector:attached.to:the:power:supply-unitii Next; disconnect:the:AC-inlet:

intalse, lift the ਦਸ ਦੇ ਸਰਕਾਰ ਦਾ ਪਾਰਟ ਹੈ। ਜਾਣ ਹੈ। ਹੈ। ਜਾਣ ਹੈ। ਹੈ। ਜਾਣ ਹੈ। ਹੈ। ਜਾਣ ਹੈ front side. Then, remove the power supply unit by pulling it forward as a whole.

# Removal from the CPU circuit board.

inward a little, lift off the video module unit.

t has legs as shown. Be careful not to damage them during removal.)

ector to the video module unit, insert it while holding the lower side of the circuit board as it is

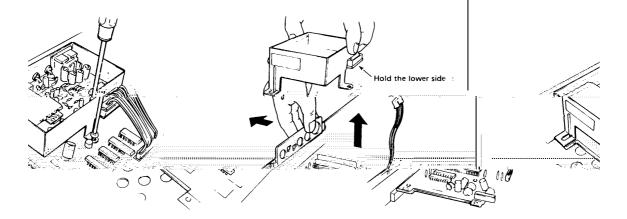

- 4) Video Module Unit

- 1 Pull out the connector

- 2 Remove two screws.

- 3 Pushing the rear panel (The video module uni

- \* In attaching the conne easily cracked.

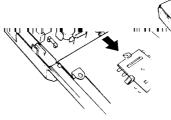

#### 5) CPU Circuit Board Removal

- 1 Remove seven screws securing the CPU circuit board in position.

- 2 Remove the side slot earth plate.

- 3 Release the two stopper claws extending from the bottom case by lifting the board a little on the front side. Then, remove the CPU circuit board by pulling it forward. Note that the in CPU circuit board is also secured in position by two stopper claws from the bottom case. The printer connector stoppers may be secured with a rubber band to facilitate servicing.

ounding plate

\* The video RAM circuit board and the main RAM circuit board are screwed to the bottom case by a greach. Follow the steps below to remove these boards.

# 6) Video RAM Circuit Board Removal

lase the board

- 1 Remove one screw securing the video modulation unit, or remove the video modulation unit. Next, relestopper claws.

- 2 Detach the video RAM circuit board from the CPU circuit board connector.

#### 7) Main RAM Circuit Board Removal

- 1 Remove one screw securing the power supply unit, or remove the power supply unit.

- 2 Remove the side slot earth plate.

d connector.

3 Next, release the board stopper claws and detach the main RAM circuit board from the CPU circuit board

#### 8) Overhauling Keyboard Unit

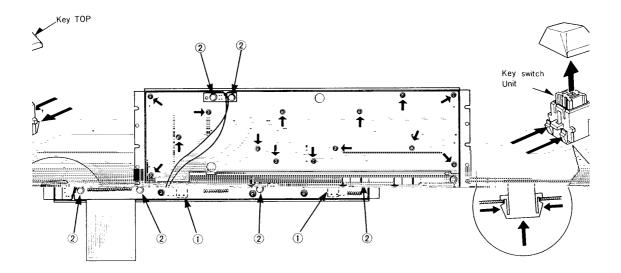

II■Desold@#564#S65FD9<u>#anolDEL</u>(#ARS#andEC(Cl90+Reyswitches=and. [[HD5#**Eon**rith**esuberircuii**nboard**a**ig\_

vet LED. Exteri

- 2 Raise the sub-circuit board by removing the six plastic plus securing the sub-circuit board and the portion CN2 and CN3 flat cables at this time ②.

- 3 Remove the switch frame by unscrewing 17 special screws.

- 4 Pull out the keytops slowly as shown.

- 5 The key switch unit can be removed by holding it on the left and right claws and pushing them inward.

# **ADJUSTMENTS**

| Adjustment            | Equipment required         | Measure at                                     | Adjust                | Readings               |

|-----------------------|----------------------------|------------------------------------------------|-----------------------|------------------------|

| +5V supply<br>voltage | DVM<br>(Digital voltmeter) | Pin #4 and 7 of<br>connector<br>CN2, CPU board | VR101<br>power supply | +5V ± 0.25V            |

| Clock<br>frequency    | Frequency counter          | Pin #6 of Z80A<br>CPU                          |                       | 3.579545MHz<br>± 500Hz |

Notes) Check AC line voltage to insure that it is specification voltage ± 10%.

The adjustment for +5V supply voltage should be made while the circuitry of the CX-5MII is connected.

### • Measurement

| Item                    |                                                                                                                                                                                                          |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conditions              | <ul> <li>Connect power circuit to CPU board.</li> <li>Apply no load to each slot (game cartridge, etc.) of CPU board.</li> <li>Don't connect peripheral equipments (printer, JOYSTICK, etc.).</li> </ul> |

| Voltage                 | +5V ± 5%                                                                                                                                                                                                 |

| Voltage to be confirmed | · –12V (1 pin) & GND: –12V ± 12.5%<br>· +12V (2, 3 pin) & GND: +12V ± 12.5%                                                                                                                              |

- Adjust VR101 so that the above listed voltages are obtained at each voltage output pin with each unit connected. Also, confirm that the output voltage is within the tolerance range even when the power voltage is 220 to 240V or 117V.

- Check to make sure that each output voltage is within the cartridge protect voltage when the micro switch of the upper slot is turned OFF (pressed) or the 9 pin circuit of CN102 is opened.

| Circuit name | Voltage | Tolerance range | Cartridge protect voltage |

|--------------|---------|-----------------|---------------------------|

| -5V          | +5V     | ± 5V            | Within 1V                 |

| +12V         | + 12V   | ± 12.5V         | Within 2V                 |

| -12V         | -12V    | ± 12.5V         | Wihtin 2V                 |

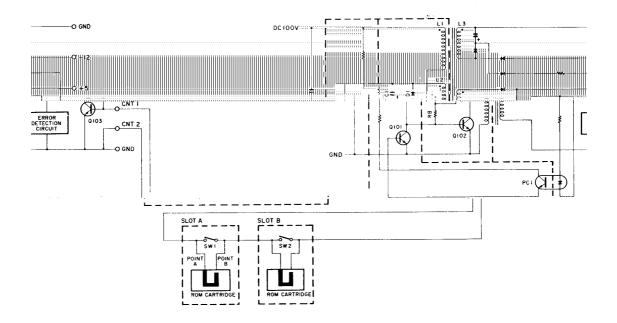

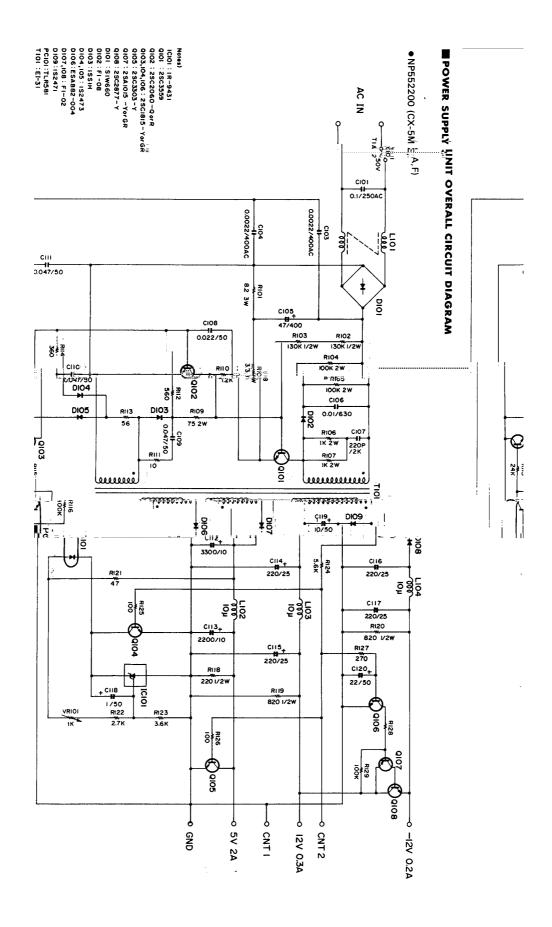

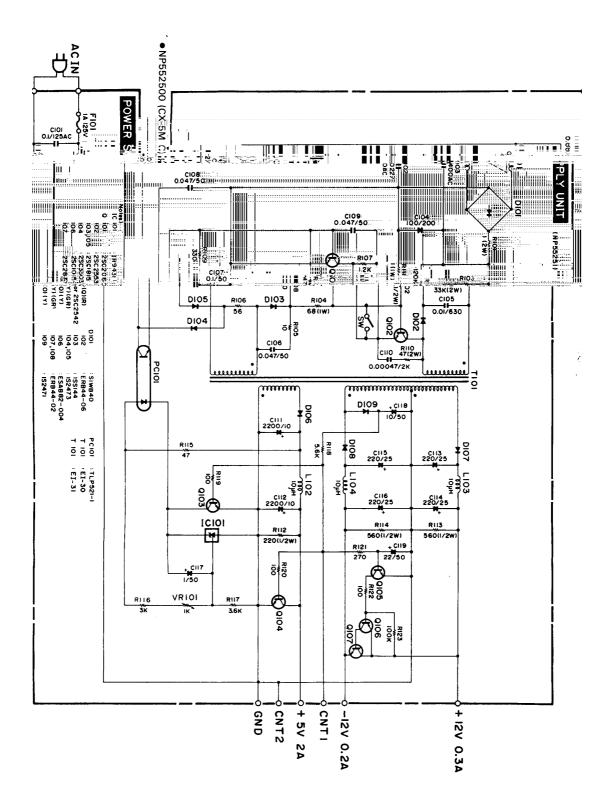

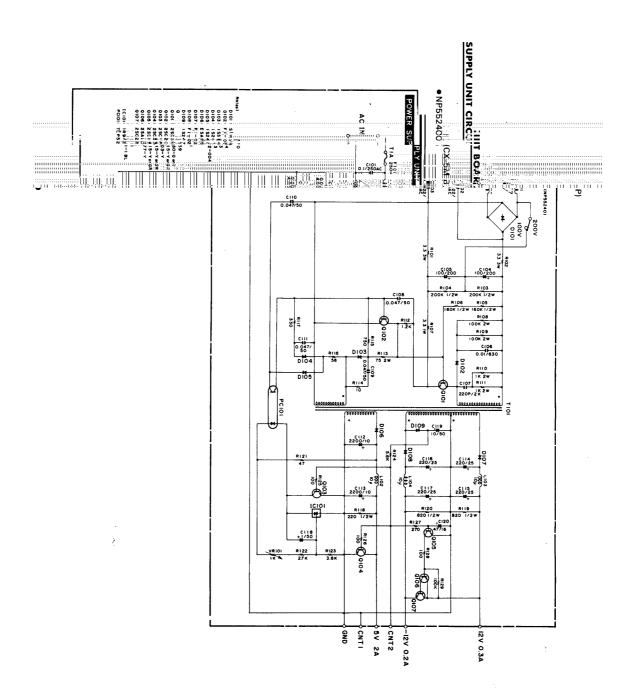

# **■ OPERATION OF POWER SUPPLY CIRCUIT**

The following is the destination and operation of the circuit.

- 1. In D1, C1 and RB are the base drive circuits, and the base current of Q102 is determined by RB.

- 2. Q101 operates as a voltage controller and cartridge protectos.

- 3. The photocomplet (VO1) reads but across the account of the control of the first that the control of the cont

- 4. SW1, SW2 connected to Q103 in the cartridge protector circuit is ON at all times.

- 5. When Q103 is ON and the ROM cartridge is set in the slot-A erroneously, SW1 is turned OFF.

Next, Q103 is turned ON, and the current flowing in the photocoupler (PC1) increases.

Then, the photocoupler (PC1) on the control circuit is turned ON to turn ON Q101.

The oscillating frequency of Q102 increases, the energy stored in L1 decreases, and output voltage lowers. When the ROM cartridge is properly set afterwards, A and B points in Fig. A are short-circuited, and voltage increases again.

# **■ OPERATION OF POWER SUPPLY CIRCUIT**

The following is the destination and operation of the circuit.

- 1. In D1, C1 and RB are the base drive circuits, and the base current of Q102 is determined by RB.

- 2. Q101 operates as a voltage controller and cartridge protectos.

- 3. The photocomplet (VO1) reads but across the account of the control of the first that the control of the cont

- 4. SW1, SW2 connected to Q103 in the cartridge protector circuit is ON at all times.

- 5. When Q103 is ON and the ROM cartridge is set in the slot-A erroneously, SW1 is turned OFF.

Next, Q103 is turned ON, and the current flowing in the photocoupler (PC1) increases.

Then, the photocoupler (PC1) on the control circuit is turned ON to turn ON Q101.

The oscillating frequency of Q102 increases, the energy stored in L1 decreases, and output voltage lowers. When the ROM cartridge is properly set afterwards, A and B points in Fig. A are short-circuited, and voltage increases again.

# LSI DATA TABLE

# • CPU (LH0080A)

| PIN NO. | PIN NAME              | 1/C ·  | ACTIVE: | FUNCTION                                                                   |

|---------|-----------------------|--------|---------|----------------------------------------------------------------------------|

| 1~5     | A11, 12, 13, 14, 15   | 0.     |         | Address bus                                                                |

| . 6     | φ                     | 1      | l       | CPU clock input (3.579545MHz) +                                            |

| 7~10    | CD4, 3, 5, 6          | 1/0 :  | 1       | Data bus                                                                   |

| 11      | VDD.                  | 1      |         | Voltage Supply +5V                                                         |

| 12~15   | CD2, 7; 0; 1          | : I/O: |         | Data bus :-                                                                |

| 16      | INT                   | l `i   | L !     | Mask-able interrupt input pin: Mode 1 is used for interrupt of MSX         |

| 1       |                       |        |         | BASIC which is input by taking the logic OR of the VDP interrupt           |

| 4       |                       | 1      | ۱,      | nutopa ('evecy,1'(60s), sersabe paetridog interrupa inopt (EXT/INT).       |

| 17      | NMI                   |        |         | Non-connect                                                                |

| 18      | HALT                  | l      |         | Non-connect                                                                |

| 19      | MREQ                  | 0      | L       | Active when the effective address for memory access is on the address bus. |

| 20      | TORQ                  | 0      | L       | Active when the effective address for the input/output port access is on   |

|         |                       |        |         | the address bus (also active when in INT or ACK cycle)                     |

| 21      | RD                    | 0      | L       | Active during the period when the CPU can receive data from the memory     |

| 1       |                       |        |         | and input/output port.                                                     |

| 22      | WR                    | 0      | L       | Active when the CPU sends data to be stored in the memory and input/       |

| 1       |                       | 1      |         | output port to the data bus.                                               |

| 23      | BUSAK                 |        |         | Pull up (+5V)                                                              |

| 24      | WAIT                  | 1      | L       | CPU remains in the wait state as long as this signal is active "L".        |

|         | İ                     |        |         | (No refresh signal is generated when in the WAIT state.)                   |

| 25      | BUSRO                 | İ      |         | Non-connect                                                                |

| 26      | RESET                 | 1      | L       | The program counter becomes "0" at the RESET input and the CPU is          |

|         |                       |        |         | initialized.                                                               |

| 27      | M1                    | 0      | L       | One "L" pulse is output at each instruction fetch cycle (also active when  |

| 1       |                       |        |         | in the INT or ACK cycle)                                                   |

| 28      | RFSH                  | 0      | L       | Active when the low order 7 bit refresh address for D-RAM is on the        |

| 1       |                       | 1      |         | address bus                                                                |

| 29      | Vss                   | 1      |         | Ground                                                                     |

| 30~40   | A0, 1, 2, 3, 4, 5, 6, | 0      |         | Address bus                                                                |

|         | 7, 8, 9, 10           |        |         |                                                                            |

# • MPS (S3527)

| PIN NO. | PIN NAME   | 1/0 | ACTIVE | FUNCTION                                                                    |

|---------|------------|-----|--------|-----------------------------------------------------------------------------|

| 1       | CMI        | 1   |        | Read signal input from cassette tape                                        |

| 2       | СМО        | 0   |        | Write output to cassette tape                                               |

| 3       | REM        | 0   |        | Cassette control signal output (motor ON/OFF control)                       |

| 4       | PRISND     | 0   |        | Software-controlled sound output                                            |

| 5       | SSGSND     | 0   |        | SSG anlog sound output                                                      |

| 6       | Vss        |     |        | OV SSG ground                                                               |

| 7       | VDPCW      | 0   |        | VDP (Video Display Processor) write timing signal output                    |

| 8       | VDPCR      | 0   |        | VDP read timing signal output                                               |

| 9       | RSEL       | 1   |        | Slot expansion address input                                                |

| 10~18   | AB15 ~ AB0 | 1   | į      | Z80A CPU address bus input (9 bits) (AB15, AB14, AB7, AB6, AB5,             |

| į       |            |     |        | AB4, AB3, AB1, AB0)                                                         |

| 19~26   | DB7 ~ DB0  | 1/0 |        | Z80A CPU data bus I/O (8 bit)                                               |

| 27      | SLT03/33   | 0   |        | Expanded slot 03 select signal                                              |

| 28      | SLT01/31   | 0   |        | Expanded slot 01 select signal                                              |

| 29      | φOUT       | 0   |        | Z80A CPU clock output                                                       |

| 30      | φIN .      | 1   | :      | Clock input (This signal is used via a buffer for clock input to other than |

|         |            | ļ   |        | the Z80A).                                                                  |

| 31      | Vss        |     |        | 0V ground                                                                   |

| 32      | RST: O     | 0   |        | Slot expansion initialization signal input                                  |

| j 33 '  | RST i      | 1.1 |        | Slot expansion initialization signal input (RESET signal input) i           |

| 2/100   | M*⁴i‡i I   | - i | 1. 1   | ZQEAUTRUI W Titaninput                                                      |

| 35      | RFSH       |     |        | Z80A CPU RFSH input                                                         |

| 36      | MREQ       | 1   |        | Z80A CPU input                                                              |

| 37      | IORQ       | 1   |        | Z80A CPU IORQ input                                                         |

| 38      | RD         |     |        | Z80A CPU RD input                                                           |

| 39      | WR         | 1   |        | Z80A CPU WR input                                                           |

| 40      | VDD        |     |        | +5V power supply                                                            |

| 45<br>46 | CAS 3                              | <u></u> |       | D-RAM CAS signal output (CAS3: SLOT #0 C000 ~ FFEE)                                                                                           |

|----------|------------------------------------|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 48 1     |                                    | )    -  |       | D-RAM CAS signal output (CAS2/E: SLOT #32:0000 ~ FFFF)  D-RAM write glable signal output  JUYS TCK FWD 1 signal or general-purpose port input |

| 49       | BACK 1                             | l i     |       | JOYSTICK BACK 1 signal or general-purpose port input                                                                                          |

| 50       | LEFT 1                             | i       |       | JOYSTICK LEFT 1 signal or general-purpose port input                                                                                          |

| 51       | RIGHT 1                            | i       |       | JOYSTICK RIGHT 1 signal or general-purpose port input                                                                                         |

| 52       | TRGA 1                             | 1/0     | */△   | JOYSTICK TRGA 1 signal or general-purpose port output (I/O by wired                                                                           |

| 53       | TRGB 1                             | 1/0     | */△   | logic) JOYSTICK TRGB 1 signal or general-purpose port output (I/O by wired logic) logic)                                                      |

| 54       | STB 1                              | 0       |       | General-purpose port output                                                                                                                   |

| 55       | FWD 2                              | 1       |       | JOYSTICK FWD 2 signal or general-purpose port input                                                                                           |

| 56       | BACK 2                             | li      |       | JOYSTICK BACK 2 signal or general-purpose port input                                                                                          |

| 57       | LEFT 2                             | i ı     |       | JOYSTICK LEFT 2 signal or general-purpose port input                                                                                          |

| 58       | RIGHT 2                            | l i     |       | JOYSTICK RIGHT 2 signal or general-purpose port input                                                                                         |

| 59       | TRGA 2                             | 1/0     | */△   | JOYSTICK TRGA 2 signal or general-purpose port output (I/O by wired                                                                           |

| 60       | TRGB 2                             | 1/0     | */△   | logic) JOYSTICK TRGB 2 signal or general-purpose port output (I/O by wired logic)                                                             |

| 61       | STB 2                              | 0       |       | General-purpose port output                                                                                                                   |

| 62       | Y10/SK                             |         | */△   | Not used (Keyboard scanning signal output (1 bit))                                                                                            |

| 63       | JIS/50                             | - 1     | *     | Keyboard layout control input                                                                                                                 |

| 64       | CAPS                               | 0       |       | CAPS LED control signal output (Direct lighting of LED possible)                                                                              |

| 65       | CODE                               | 0       |       | CODE LED control signal output (Direct lighting of LED possible)                                                                              |

| 66 ~ 73  | $\overline{x0} \sim \overline{x7}$ | 1       | •     | Keyboard return signal input (8 bits) (X6 serves as function select input on a reset.)                                                        |

| 74~83    | $\overline{Y0} \sim \overline{Y9}$ | 0       |       | Keyboard scanning signal output (10 bits)                                                                                                     |

| 84       | CS1                                | o       | 1 - 1 | ROM select signal output (4000 ~7FFF)                                                                                                         |

| 85       | CS2                                | 0       |       | ROM select signal output (8000 ~ BFFF)                                                                                                        |

| 86       | CS12                               | 0       |       | ROM select signal output (4000 ~ BFFF)                                                                                                        |

| 87       | SLT1                               | 0       |       | Slot select signal output (SLOT #1)                                                                                                           |

| 88       | SLT2                               | 0       | 1     | Slot select signal output (SLOT #2)                                                                                                           |

| 89       | SLT3/30                            | 0       | 1     | Slot select signal output (SLOT #3)                                                                                                           |

| 90       | VDD                                |         | 1 1   | +5V power supply                                                                                                                              |

| 91       | BUSY                               | 1       | 1 • 1 | Printer status input                                                                                                                          |

| 92~99    | PD87 ~ PD80                        | 0       |       | Print data output (8 bits)                                                                                                                    |

| 100      | PSTB                               | 0       |       | Printer strobe output                                                                                                                         |

Note) \* With pullup resistor ( ≃22K) △ Open Drain (Pull Down) OUTPUT

the second

# • VDP (V9938)

| PIN NO. | PIN NAME       | 1/0 | FUNCTION                                                              |    |

|---------|----------------|-----|-----------------------------------------------------------------------|----|

| 1       | GND            |     | Ground                                                                |    |

| 2       | DHCLK          | 0   | Not used                                                              |    |

| 3       | DLCKL          | 1/0 |                                                                       |    |

| 4       | VDS            | 0   | Not used                                                              |    |

| 5       | HSYNC          | 1/0 | High level (high to middle): output, low level (middle to low): input |    |

|         |                | İ   | High: Non-HSYNC timing or color burst timing                          |    |

|         |                |     | Middle: HSYNC timing or color burst timing                            |    |

| İ       |                |     | Low: HSYNC input                                                      |    |

| 6       | CSYNC          | 1/0 | High level: composite SYNC output, low level: VSYNC input             |    |

| 7       | BLEO           | 0   | Not used                                                              |    |

| 8       | CPU CLK        | 0   | 1/6 X'TAL frequency output                                            |    |

| 9       | RESET          | 1   | MSX-VIDEO circuit initialization                                      |    |

| 10      | YS             | 0   | Not used                                                              |    |

| 11      | CBDR           | 0   | Not used                                                              |    |

| 12~19   | C7 ~ C0        | 1/0 | Not used                                                              |    |

| 20      | GND            | İ   | DAC ground                                                            |    |

| 21      | VIDEO          | 0   | Not used (Composite video signal output)                              |    |

| 22      | G              | 0   | Linear RGB signal output                                              |    |

| 23      | R              | 0   | Linear RGB signal output                                              |    |

| 24      | В              | 0   | Linear RGB signal output                                              |    |

| 25      | INT            | 0   | CPU interrupt request signal output (low: Interrupt-request)          |    |

| 26      | LPS            | 1   | Not used                                                              |    |

| 27      | LPD            | 1   | Not used                                                              |    |

| 28      | MODE 1         | 1   | CPU interface mode select signal                                      |    |

| 29      | MODE 0         | 1   | CPU interface mode select signal                                      |    |

| 30      | CSW            | 1 1 | CPU-VDP write strobe                                                  |    |

| 31      | CSR            | 1   | CPU-VDP read strobe                                                   |    |

| 32      | CD7            | 1/0 | CPU-data bus                                                          |    |

| 33      | VBB            | 0   | Circuit board voltage                                                 |    |

| 34~40   | $CD0 \sim CD6$ | 1/0 | CPU data bus                                                          |    |

| 41~48   | RD0 ∼ RD7      | 1/0 | VRAM data bus                                                         |    |

| 49~56   | AD0 ∼ AD7      | 0   | VRAM address bus                                                      |    |

| 57      | R/W            | 0   | VRAM write strobe                                                     |    |

| 58      | Vcc            |     | +5V power supply                                                      |    |

| 59      | CASX           | 0   | Not used                                                              |    |

| 60      | CAS1           | 0   | Not used                                                              |    |

| 61      | CASO           | 0   | VRAM column address strobe                                            |    |

| 62      | RAS            | 0   | VRAM low address strobe                                               | ** |

| 63      | XTAL 1         | 1   | X'TAL connection (Externally oscillated clock is input to this pin.)  |    |

| 64      | XTAL 2         | 1   | X'TAL connection (Externally oscillated clock is input to this pin.)  |    |

Note) \* With pullup resistor (  $\simeq$  22k)  $\triangle$  Open Drain (Pull Down) OUTPUT

# • 16Kbit × 4 DRAM (MB81416-12)

| PIN NO. | PIN NAME       | 1/0 | ACTIVE | FUNCTION                                                                                                                          |

|---------|----------------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| 1       | ŌE             | 1   |        | Output enable                                                                                                                     |

| 2,3     | DQ1, DQ2       | 1/0 |        | Data output                                                                                                                       |

| 4       | WE             | 1   | 1 1    | Write enable, write mode at active "L"                                                                                            |

| 5       | RAS            | 1   |        | Lower address strobe                                                                                                              |

| 6∼8     | A6, 5, 4       | 1   |        | Address input                                                                                                                     |

| 9       | VDD            |     |        | Voltage Supply +5V                                                                                                                |

| 10~14   | A7, 3, 2, 1, 0 | 1   |        | Address input                                                                                                                     |

| 15      | DQ3            | I/O |        | Data output                                                                                                                       |

| 16      | CAS            | 1   |        | Column address strobe                                                                                                             |

| 17      | DQ4            | 1/0 |        | Data output                                                                                                                       |

| 18      | Vss            |     |        | Ground                                                                                                                            |

|         |                |     |        | Note) MB81416 is an N channel MOS RAM consisting of 16384 word x<br>4 bit. RAS only refresh type, write cycle (early write) type. |

# • 64Kbit DRAM (MB8264)

| PINA<br>1<br>2<br>3<br>3<br>1<br>4<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | PINNAME  O In  WE  AVE  VE  VE  VE  VE  VE  VE  VE  VE |              | Count address strope  J. Cower address strope  Address bus input:  Data potiput  Count address strope  Ground |  |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------|--|

| 1 2                                                                                                                | : VDD CLOCK                                            | 1            | #5V.power Timing clock for synchronizing with OPE                                                             |  |

| 3                                                                                                                  | : GND                                                  | _            |                                                                                                               |  |

| 4                                                                                                                  | DATA                                                   | , i          | Tone sirial data                                                                                              |  |

|                                                                                                                    | 1                                                      | in   t -<br> | ্লি Sampling data (for LR sepārator): ্লি<br>১৮লিছিসমূৰ্যামত ব্যুৱন্তিটাটা মিংলত্ৰ্যুৱন্তিল এ ব               |  |

| 7                                                                                                                  | ICL                                                    | 1            | Initial clear                                                                                                 |  |

| 8                                                                                                                  | GND                                                    | -            | Ground for analog                                                                                             |  |

| 9                                                                                                                  | CH1                                                    | 0            | 1CH (L-CH) analog signal                                                                                      |  |

| 10                                                                                                                 | CH2<br>COM                                             | 0            | 2CH (R-CH) analog signal Offset control                                                                       |  |

| 11                                                                                                                 | To BUF                                                 | 0            | Offset control                                                                                                |  |

| 13                                                                                                                 | Mid-point                                              | 0            | Offset control                                                                                                |  |

| 14                                                                                                                 | BIAS compensation                                      | o            | Offset control                                                                                                |  |

| 15                                                                                                                 | BIAS                                                   | 0            | Offset control                                                                                                |  |

| 16                                                                                                                 | GND                                                    | _            |                                                                                                               |  |

# • MKS (YM2148)

| PIN NO. | PIN NAME         | 1/0 | FUNCTION                                                                | REMARKS                                             |

|---------|------------------|-----|-------------------------------------------------------------------------|-----------------------------------------------------|

| 1       | Vss              |     | Ground                                                                  |                                                     |

| 2~4     | $A_0 \sim A_2$   | 1   | Selection signal for internal registers                                 |                                                     |

| 5       | cs               | 1   | Chip select                                                             |                                                     |

| 6       | WT               | 1   | Write request for data from CPU                                         |                                                     |

| 7       | RD               | 1   | Read request for data from CPU                                          |                                                     |

| 8       | ОРМ              | 0   | Address decode out to OPM                                               | Output when $A_0$ to $A_1$ address input is 0 or 1. |

| 9~16    | $st_0 \sim st_7$ | 0   | Used as strobe output to keyboard                                       | Latch output ports in 2nd address                   |

| 17      | VDD              |     | +5V power                                                               |                                                     |

| 18      | RXD              | 1   | MIDI serial data                                                        |                                                     |

| 19~26   | $sd_0 \sim sd_7$ | 1   | Data input port                                                         | Data input ports to 2nd address                     |

| 27      | TXD              | 0   | MIDI serial data                                                        |                                                     |

| 28~35   | $D_0 \sim D_7$   | 1/0 | 3-state data bus I/O ports                                              |                                                     |

| 36      | VR               | ı   | VECTOR ADDRESS REQUEST                                                  | Used for Z-80 MODE 2, IRQ                           |

| 37      | IRQ              | 0   | Interrupt request generated when receiving and transmitting MIDI signal | Maskable                                            |

| 38      | ĪC               | 1   | "L" reset data IRQ "H", OPM "H"                                         | ST0 ~ ST7 "H", D0 ~ D7 "Hi impedance"               |

| 39      | φΑ               | 1   | Clock for MIDI baud rate generation                                     |                                                     |

| 40      | φ                | . 1 | CPU Master clock for synchronizing with CPU                             |                                                     |

# • OPM (YM2151)

| PIN NO. | PIN NAME                   | 1/0 | FUNCTION                                    | REMARKS |

|---------|----------------------------|-----|---------------------------------------------|---------|

| 1       | Vss                        | _   | Ground                                      |         |

| 2       | ĪRQ                        |     | Interrupt request output port               |         |

| 3       | <del>IC</del>              | 1   | "L" reset                                   |         |

| 4       | $A_0$                      | 1   | Selection signal for internal register      |         |

| 5       | A <sub>0</sub><br>WT<br>RD | 1   | Write request for data from CPU             |         |

| 6       | RD                         |     | Read request for data from CPU              |         |

| 7       | CS                         | 1   | Chip select                                 |         |

| 8       |                            |     | Not used                                    |         |

| 9       | CT1                        | 0   | Signal for switching voice synchesis filter |         |

|         |                            |     | characteristics                             |         |

| 10      | $D_0$                      | 1/0 | 3-state data bus I/O port                   |         |

| 11      | Vss                        | -   | Ground                                      |         |

| 12~18   | $D_1 \sim D_7$             | 1/0 | 3-state data bus I/O ports                  |         |

| 19      | SH1                        | 0   | Signal for separating L and R               |         |

| 20      | SH2                        | 0   | Signal for separating Land h                |         |

| 21      | $s_0$                      | 0   | Serial data for sound source (L, R)         |         |

| 22      | VDD                        | _   | +5V power                                   |         |

| 23      | φ1                         | 0   | Clock for DAC synchronization               |         |

| 24      | φ                          | 1   | CPU Master clock for synchronizing with CPU |         |

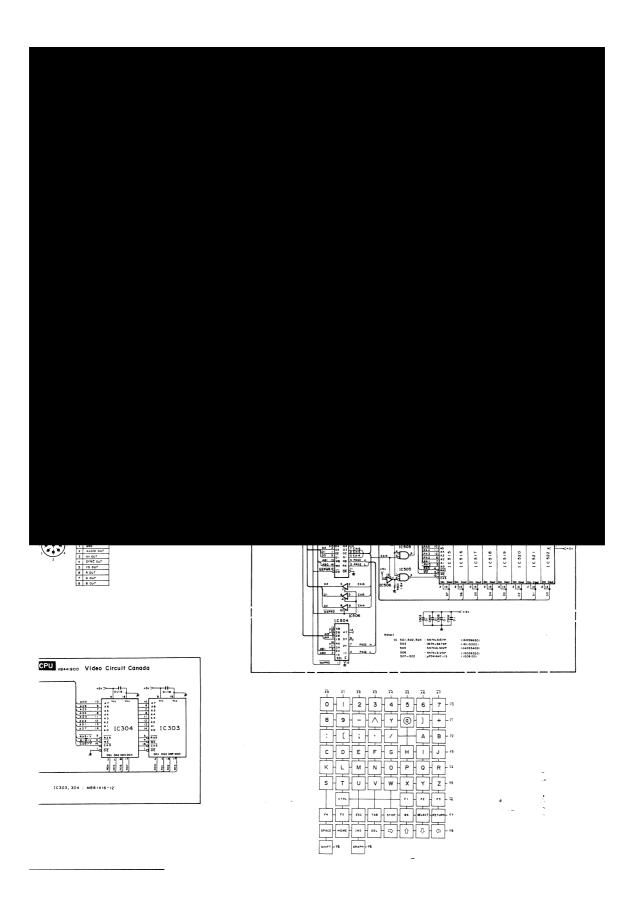

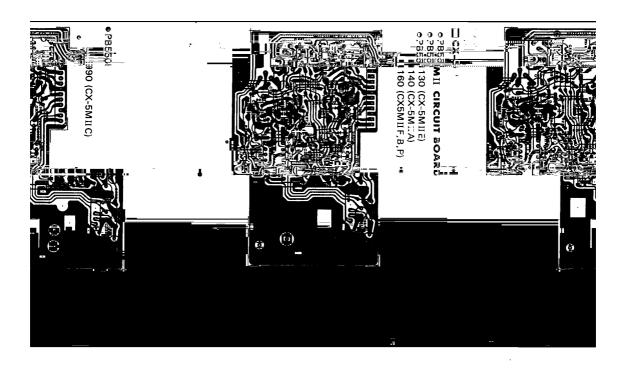

# LSI PIN CONFIGURATION

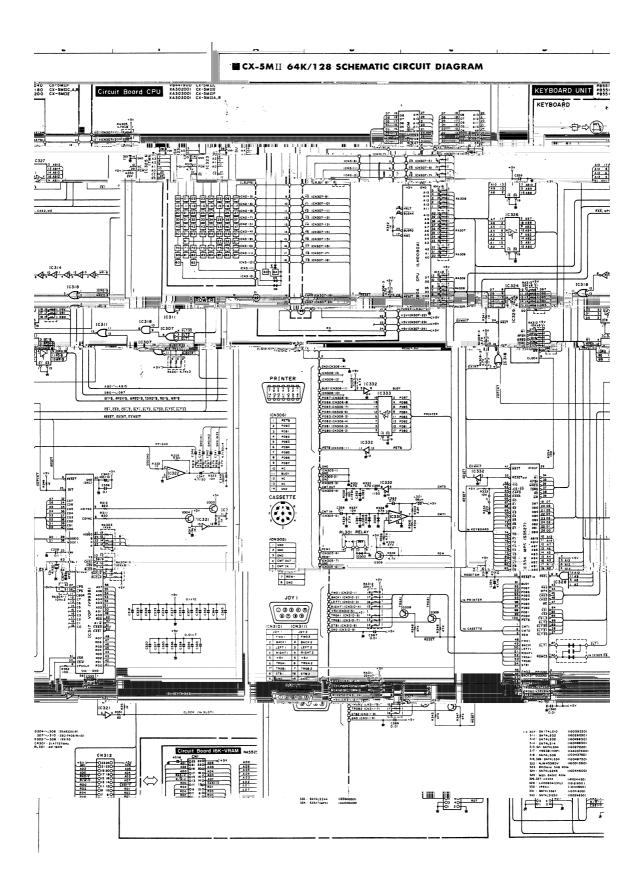

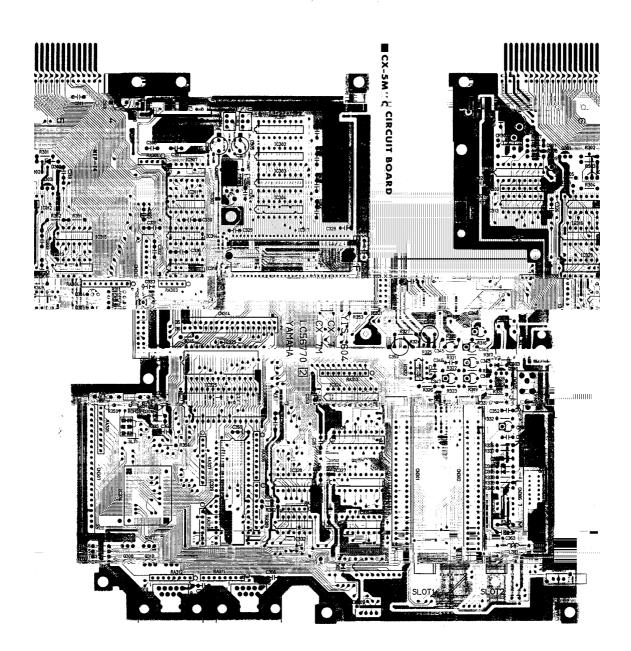

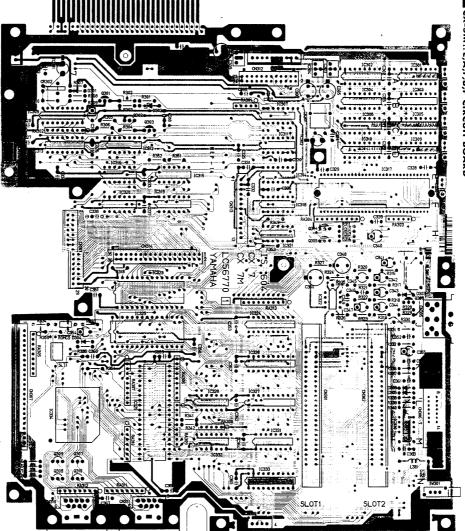

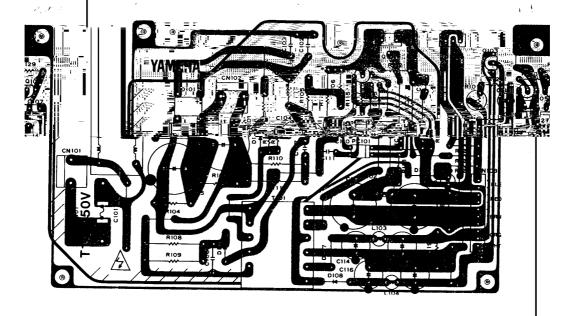

64K DRAM CIRCUIT BOARD

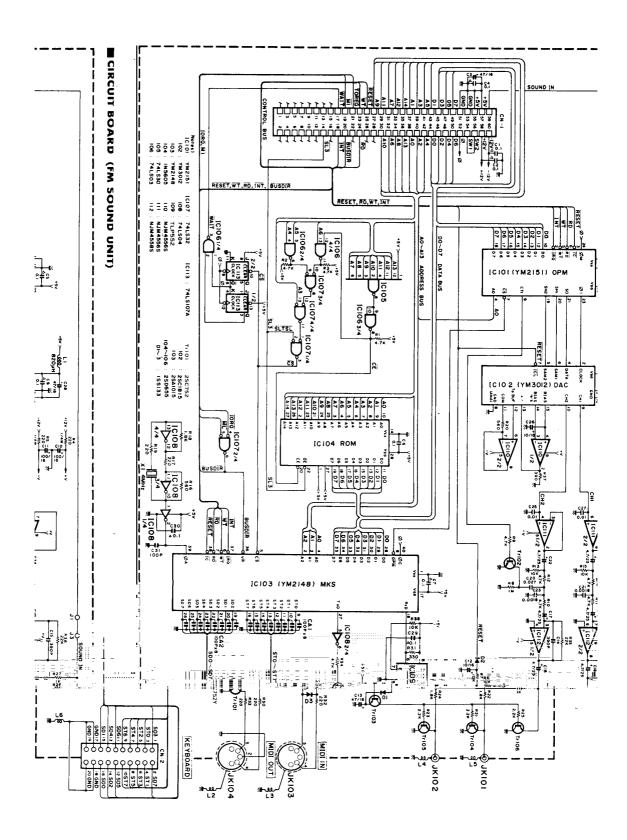

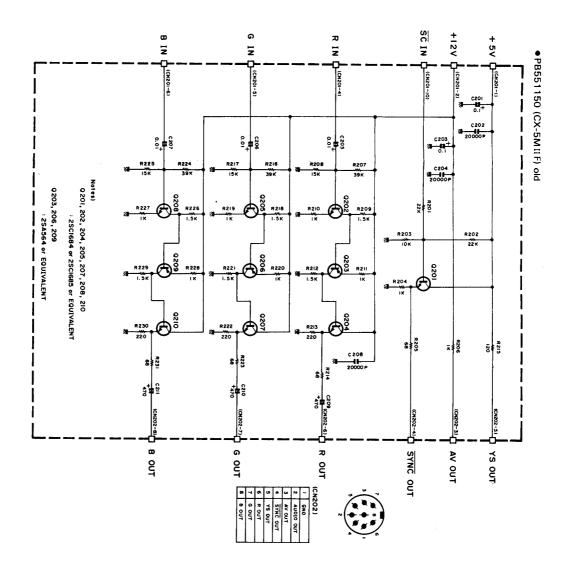

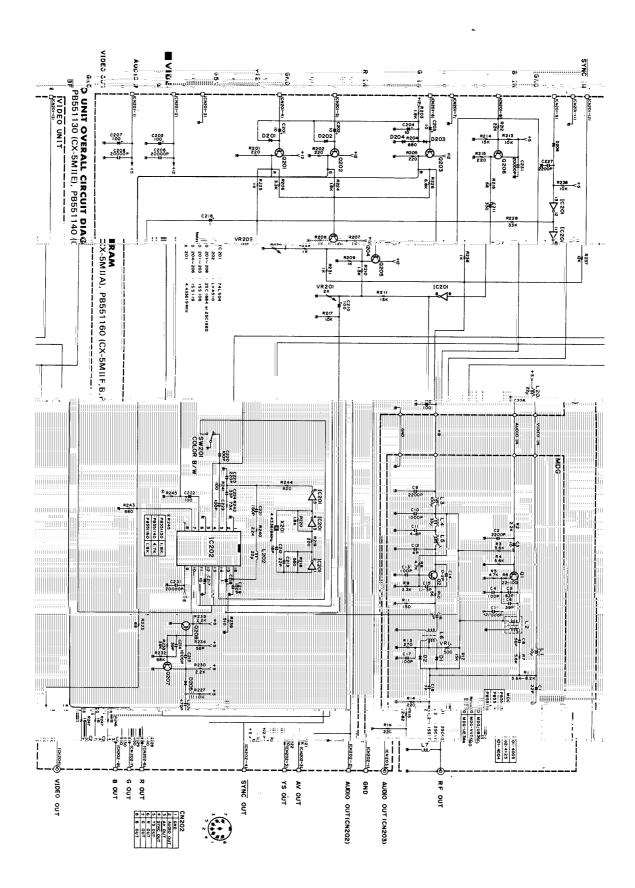

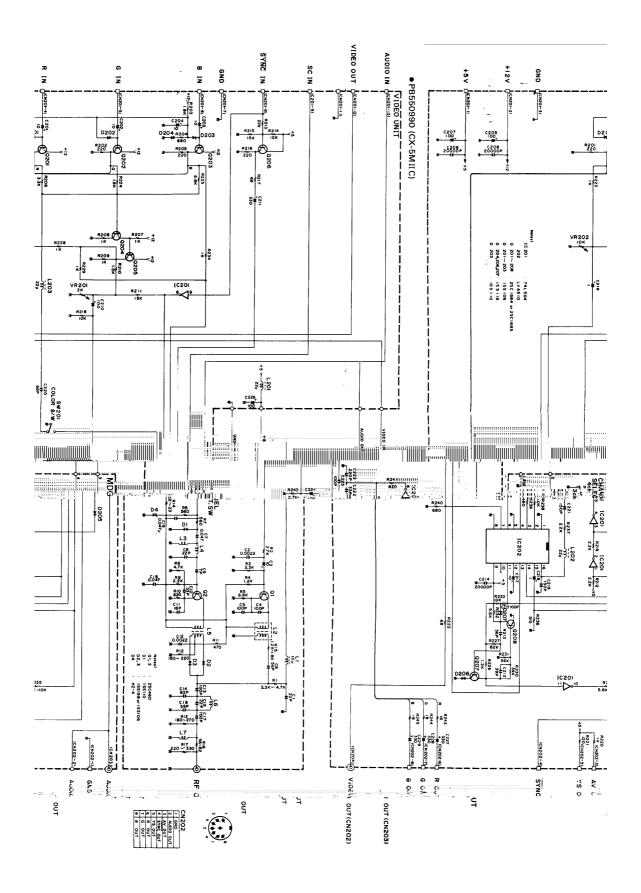

CIRCUIT BOARD (FM SOUND UNIT)

● PB551150 (CX5MIIF) old

# ■ POWER SUPPLY UNIT CIRCUIT BOARD

● NP552400 (CX-5M B,P)

● NP552500 (CX-5M C)